PCB的测试结构和测试类型

任何高速设计的一个重要部分是确保可以在制造和操作过程中成功对其进行测试。由于这些测试是在PCB设计过程的下游进行的,因此通常没有正确,彻底地将它们视为该过程的一部分。本文将介绍测试过程设计的两个重要方面:在电路板上创建测试结构(又称为测试点连接),并描述测试本身以及测试点如何连接到用于测试的各种设备。

本文的第1部分将描述访问各种测试设备所必需的测试结构,而第2部分将介绍如何将测试结构连接到设备,以便可以确认连通性测试的结果。

PCB测试流程

PCB测试过程的目标有两个:确认PCB是否按规定运行并且给定批中的所有PCB都满足此要求。

为了确定当今PCB测试过程的“状态”,解决测试的历史记录很有用。传统的裸板PCB测试涉及将PCB的网表测试为CAD生成的网表,以确保没有开路或短路。此后,有必要确保外层电镀的质量能够成功地承受组装过程。通常是从大量PCB中抽取一个PCB(称为焊料样品)并对其进行焊料测试来完成的。另外,PCB制造商可能已经从其中一个PCB上锯下了一块,然后对其进行了微截面测试,以确保正确地进行孔的镀铜。如果上述所有测试均为OK,则可将整批PCB PASS使用。

随着逻辑电路速度的提高,还需要解决一些其他因素,包括:

- 确保信号走线的阻抗在公差范围内。

- 确保每个电源子系统的平面间电容都足够。

- 确保所有电介质均具有正确的介电常数,以使传播速度符合规定。

- 确保所有PCB层的顺序正确。(在当今的制造环境中,批次中只有一个PCB的层顺序可能是错误的)。

在制造过程中执行测试的三个地方:

- 裸板测试。

- 组装板测试。

- 维修中心测试。

确定所需的测试结构

高性能PCB最明显的测试结构是阻抗Test Traces。必须为每个具有相关阻抗规范的信号层添加此迹线。另外,需要一种方法来测量每个电源电压的平面电容。还需要一种方法来确保所有层都在PCB叠层中的适当位置。它们具有正确的厚度,并且将它们隔开的电介质具有正确的厚度和玻璃样式。考虑到所有这些元素,必须创建以下测试结构:

- 阻抗Test Traces。

- 电源和接地平面对的接入点。

- 一种确保正确堆叠图层的方法。

测试结构应放置在哪里?

除了创建正确的测试结构外,还需要确保其正确放置。传统上,将这些结构放置在特殊的测试试样上。该试样不是PCB本身的一部分,而是内置在板制造面板周围的材料中。此过程的优势在于,可以将样板带到实验室进行分析,而无需从大量的任何PCB中切割样品。可以对这些试样进行标准化,以加快测试过程,这对PCB制造商而言是一件好事。图1是典型的测试试样,仅包含阻抗测试痕迹。

图1.典型的测试样品

测试试样的问题在于,无法保证该试样内的走线宽度与打算代表的PCB每一层的走线宽度相同。我们已经看到了这样的情况:测试样板测量了一组阻抗,而PCB上的阻抗却完全不同。这是由于在创建样品图稿时,制造商方面存在CAD错误。另一个问题是,测试样板在最终制造时可以与PCB分离,并且在需要时通常不可用。我们已被要求对PCB进行组装后进行故障排除,并且样品在组装过程中已存储在其他地方。这导致没有必要的可追溯性来解决设计问题。

测试结构示例

专用测试样品的上述缺点远远超过了它们的优点。因此,我们发现最好的方法是将测试结构包括在PCB本身的内部。这种方法的明显优势是:

- 测试结构始终与它们打算代表的PCB一起使用。

- 测试结构中的功能由PCB设计人员而非PCB制造商创建。

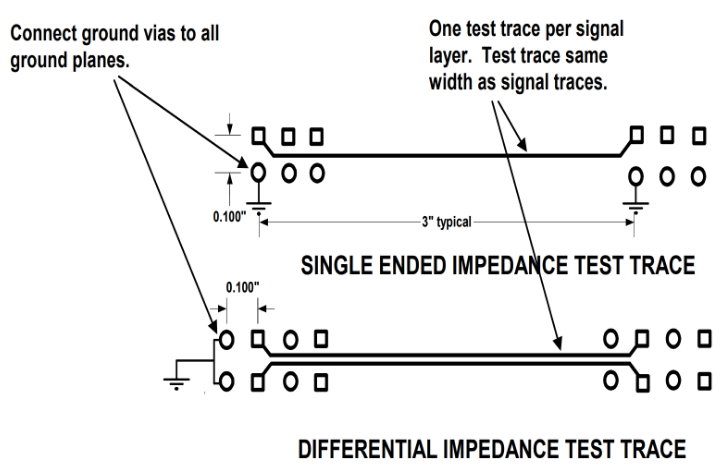

阻抗测试结构。图2显示了一种设计阻抗测试走线的方法。该图显示了单端阻抗测试结构和差分测试结构。如果PCB具有在其上控制阻抗的八个信号层,则可以扩展结构以为每一层提供测试结构。

图2.阻抗测试样品图例

测试末端的通孔的间距和大小很重要。为了允许使用标准阻抗测试探针,走线末端的通孔与其指定的接地通孔之间的距离需要为100-mil(2.54毫米)。钻孔的直径必须为30-mil(0.762毫米),以使探头正确安装。在图2中,走线的长度为3英寸(7.62厘米),是直的,两端都有通孔。

(它们仅需1英寸长(2.54厘米)即可获得精确的阻抗测量。)如果信号层上没有足够的空间使测试走线保持笔直,则弯曲该信号就可以了。同样,虽然不必在测试走线的两端都具有访问过孔,但是很方便。

图3中的照片显示了两种实现PCB测试走线的方法。在图的左侧示例中,每个测试走线都有一个接地过孔。右侧的示例在中心处有一个接地孔,并共享了四个Test Traces。两种都是实现阻抗测试走线的可接受方法。保持100-mil的孔间距和30-mil的钻头直径很重要,以便于测试。同样,每个Test Traces在丝网印刷中都带有其层号标记。这是进行实际测试的重要因素。

图3.实现阻抗测试走线的方法

顺便说一句:解决以下问题:“Test Traces的“接地”孔应连接到什么平面?我们可以再次参考图3。在图的右侧,有四个测试走线过孔围绕着一个“接地”过孔。在这里,常见问题变成:“为了获得准确的阻抗读数,TDR(时域反射计)地线是否需要连接到被测走线正下方的平面”?

为了解决这个问题,我们在所有PCB中都建立了测试结构,这些结构用于检查本书两卷中提到的各种经验法则。在每种情况下,都有一种类似于图3所示的测试结构,但是Test Traces连接到中间过孔,四个周围的过孔中的每一个都连接到PCB中的不同平面。当TDR连接到四个“接地”通孔中的任何一个时,测得的阻抗都是相同的。这是因为所有平面都通过平面间电容或组件的接地过孔以测量所涉及的频率“短路”在一起。

电源平面和旁路电容器的阻抗测试结构。图4说明了如何设计用于测量电源层和旁路电容器阻抗的接入点。

图4.在连接电容器的情况下测量电源平面的测试结构

这项重要的测试可以验证去耦电容器的数量对于每个电源电压都是正确的。PCB上的每个电源电压都需要其中两个测试访问点。这两个结构应至少相距一英寸放置,并标明它们连接的电压。一方面允许将信号注入到平面电容器中,另一方面允许对所得电压进行测量

堆叠条纹

图5所示的堆叠条纹测试结构用于检查PCB构造方式的几件事。

图5.堆叠条带

图5.堆叠条带

沿着PCB的一条边缘绘制了铜带,以便从面板上切下PCB时,肉眼可见。请注意,每一层中的条带都比上面的条带更长。通过这种阶梯式构造,可以确定所有层的顺序正确。可以很容易地观察到,越向下进入PCB,每一层的阶梯越长。有一个合理的问题要问,它们怎么可能会出现故障。实际上,设计和制造过程中有很多地方可以混合各层的顺序。一种是在准备用于蚀刻PCB层的照相工具,而另一种是在层压过程中实际放置各个层的过程中。图6是24层PCB中堆叠条纹的照片,显示了这种混合。第22层应位于第11层,第11层应位于第22层。发生这种情况的原因是,在准备Gerber数据时,CAD操作员错误地标记了CAD文件。制造商只是遵循了错误的顺序。如果已组装好该PCB,它将无法正常工作。没有堆积的条纹,就不可能确定哪里出了问题。

图6.层叠不正确的PCB

堆叠条组中的第二个特征是绘制了一小段迹线,以便当从面板上切下PCB时,可以看到其末端。该迹线绘制为5--mil宽(127微米)。通过测量实际的蚀刻宽度,可以确定信号层是否被正确蚀刻,并且没有被过度蚀刻或蚀刻不足。使用此尺寸和堆叠尺寸,可以对阻抗不在规格范围内的问题进行故障排除,并确定需要采取的纠正措施。

图7.堆叠条带的放大图

最后,堆叠条纹可让您通过测量介电层和铜层的厚度来检查PCB的整体。图7是一组实际的堆叠条纹的放大图,显示了每个介电层中的玻璃纤维,铜的厚度以及从PCB伸出的5-mil迹线。这样就可以对堆栈进行全面审核,而无需进行破坏性测试。最重要的是,这些功能是每块PCB的一部分,因此很容易在组装完PCB后很长时间检查横截面和阻抗。

提出堆叠条带时提出的一个反对意见来自于旧标准,即“在PCB的边缘不允许有裸露的铜。” 该标准的实际读取方式是,不允许将附着在PCB内部任何电路上的铜暴露在PCB边缘。通过确保这些铜条与PCB本身内部的所有电路隔离,可以轻松满足此要求。添加上述测试结构几乎不会增加成本,甚至不会增加成品PCB的成本。唯一的实际成本是PCB设计人员必须投入时间来将这些功能添加到每个新的PCB文件中的时间。根据我们的经验,CAD部门在设计第一个结构时很慢,但是一旦获得了一定的经验,此任务就几乎不会增加设计时间。

没有测试结构的代价

从到目前为止的所有讨论中,没有测试结构的成本应该很清楚。但是,在许多情况下,成本并不明显。如果没有测试结构也没有办法来隔离板故障,如不正确的阻抗,一个错叠层,所述玻璃纤维错误或错误的铜厚度。这些未发现的错误归为“片状” PCB广泛而令人沮丧的组。结果,没有采取纠正措施的机制。

如果图6中的PCB上没有使用堆叠条纹,那么制造商将在PCB上组装价值约5,000美元的零件。它永远不会正常工作。此外,负责调试的人员将花费无数的时间,而没有取得积极的成果。那值多少钱?也许整个程序都将面临风险,但是增加一些“免费”的堆叠条带将防止这种情况的发生。

测试结构导致的故障示例

图6中的PCB是使用测试结构捕获的故障的最佳示例之一。(在这种情况下,所有阻抗都是正确的,因为交换的层是电源和接地层)。通过测试结构发现的一个不太明显的故障是在物料清单上标注了错误类型的旁路电容器的组件。并且,如上所述,不正确的阻抗值是测试结构捕获的其余内容。

使用测试结构有什么缺点吗?

除了制造商和不习惯看到这些测试结构的其他人所展示的惊喜之外,将它们构建到PCB设计中也没有缺点。有时有人声称在拥挤的PCB上没有足够的空间容纳它们。根据我们的经验,一直都有空间。可能需要设计师多加一点想象力,但是总有空间。图8是PCMCIA卡的图片,其顶部边缘有堆叠条纹。

图8.带有堆叠条的PCMCIA PCB

概括

对于工程师来说,将测试结构设计到PCB和制造商中以构建它们只需要很少的时间和成本。但是,长期节省可能是可观的,并且可能意味着整体产品成功与失败之间的差异。